# **Engineered SOI substrates for RF applications**

# - current success and future perspective -

### Prof. Jean-Pierre Raskin

Institute of Information and Communication Technologies, Electronics and Applied Mathematics (ICTEAM) **Université catholique de Louvain (UCLouvain)** 1348 Louvain-la-Neuve, Belgium

Email: jean-pierre.raskin@uclouvain.be

The 10<sup>th</sup> anniversary of Incize, Castle Terblock, Overijse, Belgium, 2024

# Nanoelectronics – challenges at different levels ...

[J.-P. Raskin, Solid-State Electronics, 2016]

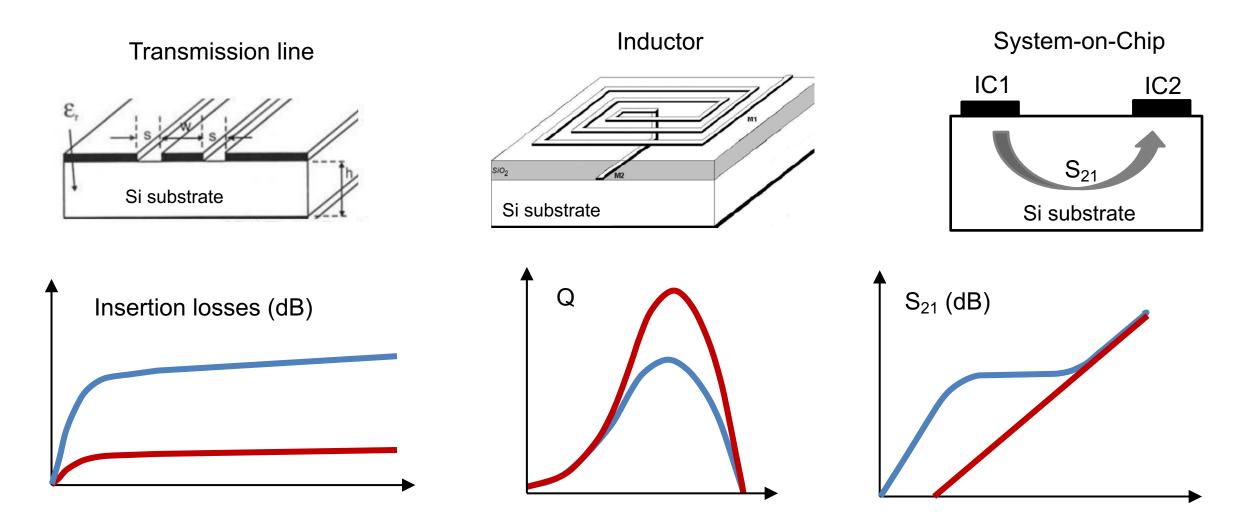

# **Need for high resistivity Si substrate**

Standard resistivity (10 Ω.cm)

High resistivity (10 k $\Omega$ .cm)

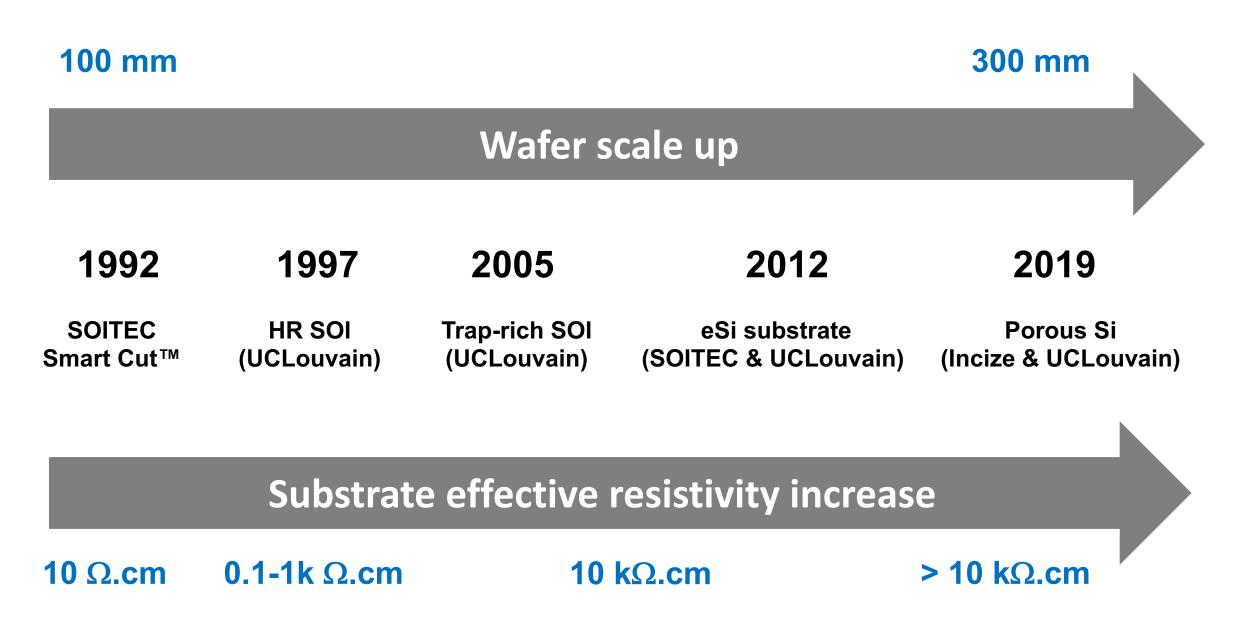

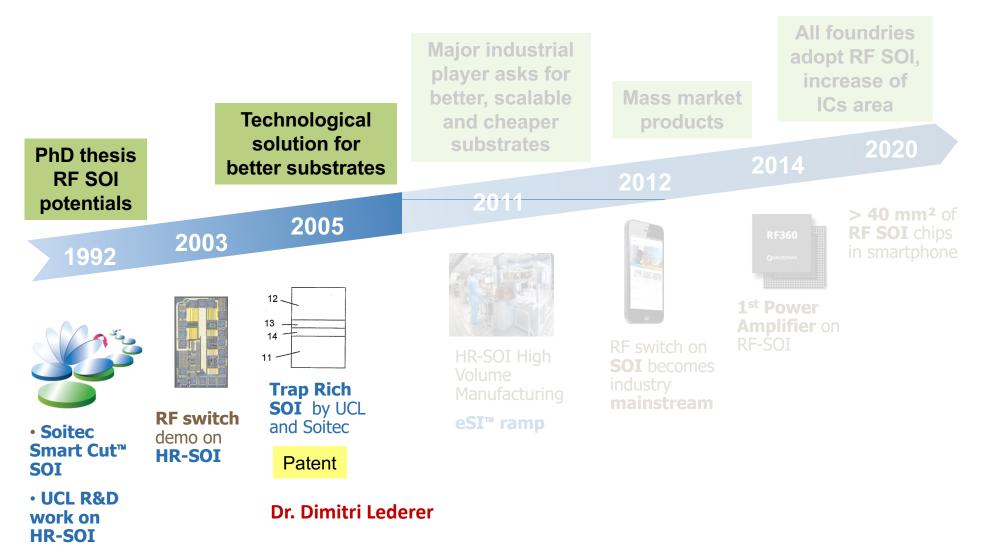

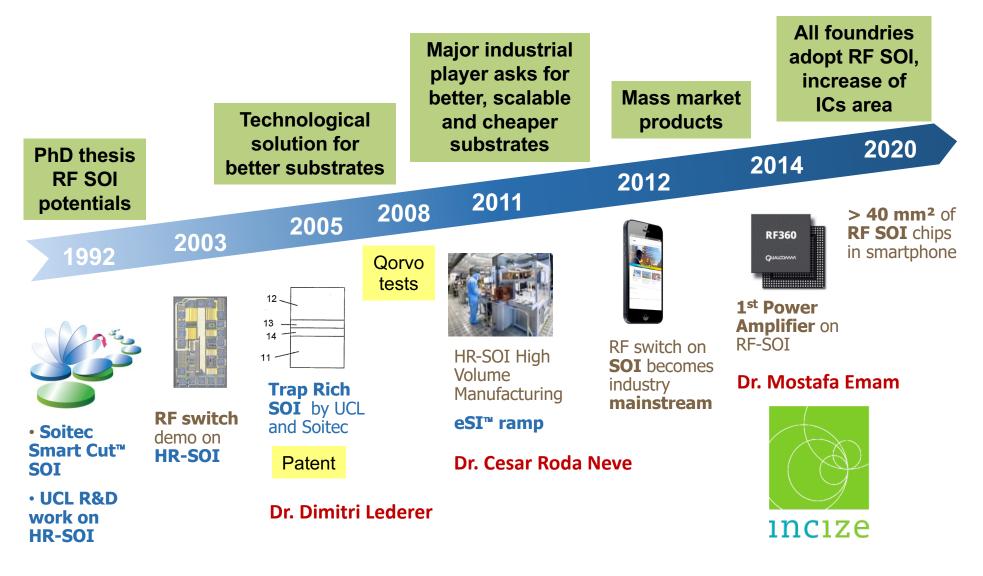

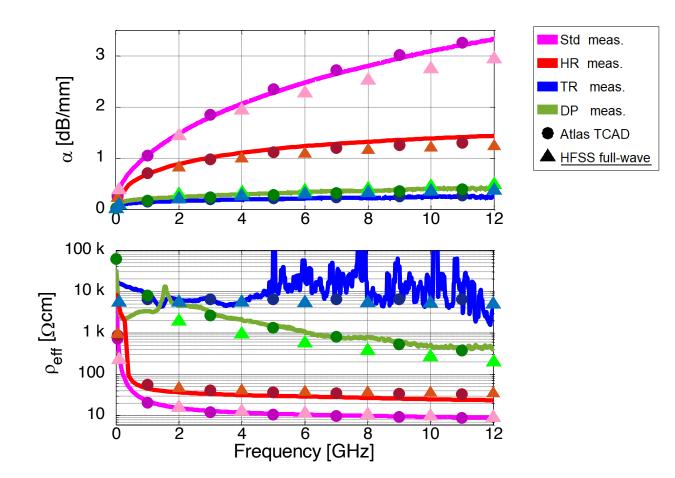

## **RF-SOI substrates: State-of-the-Art**

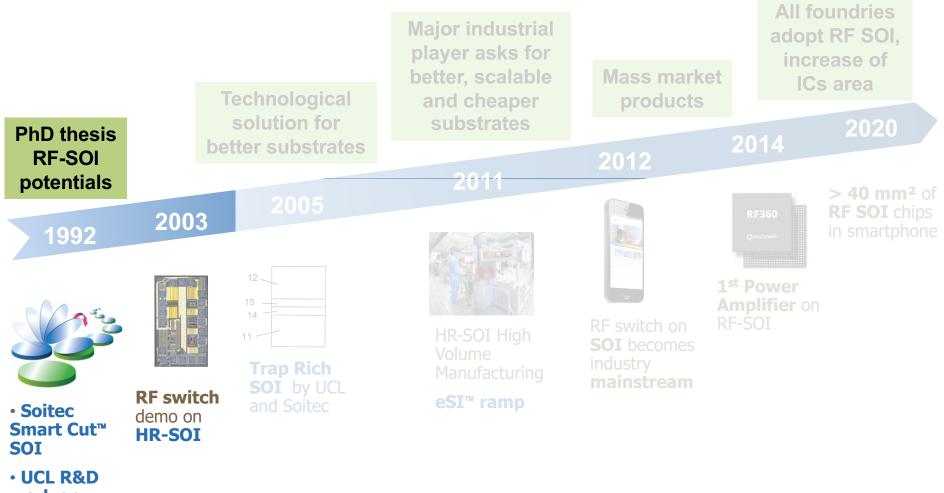

### **First steps towards RF-SOI**

work on HR-SOI

### 2004: Question from SOITEC to UCLouvain

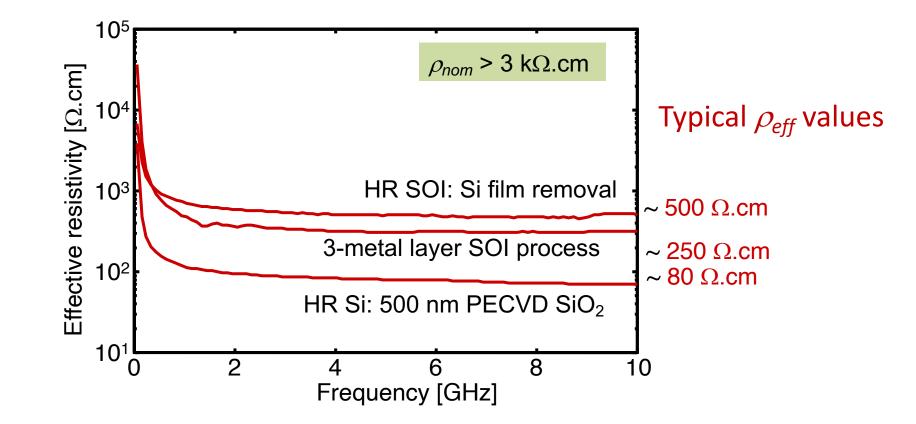

- Effective resistivity depends on process

- Effective resistivity is lower than 3 kΩ.cm

WHY?

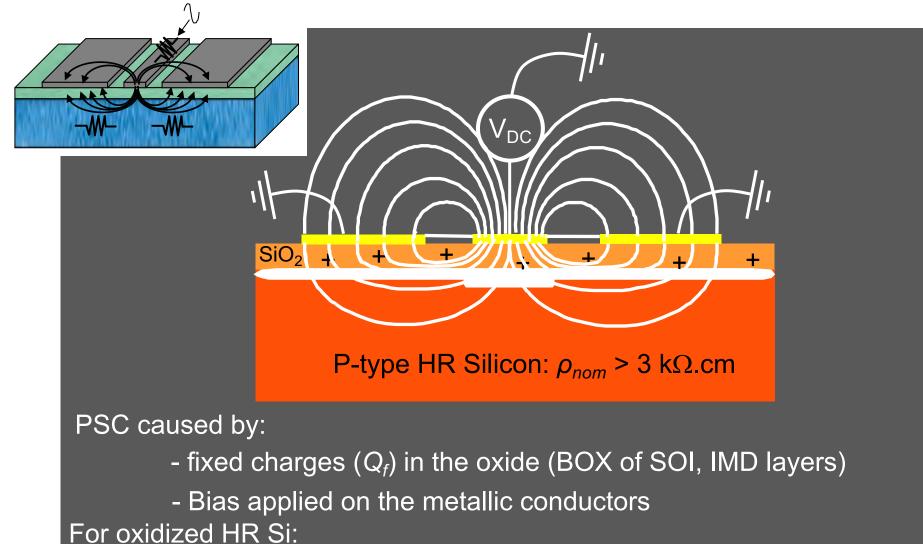

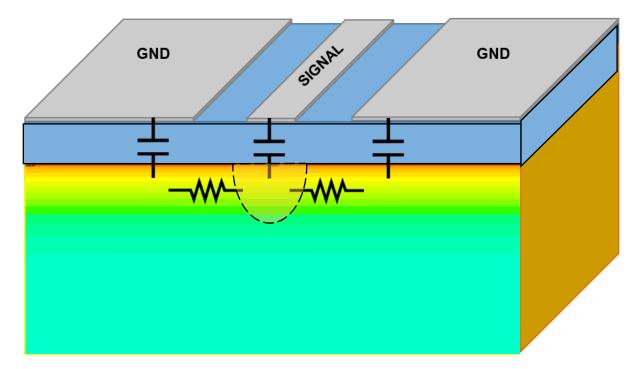

### **Parasitic Surface Conduction (PSC)**

- Effective resistivity lower than nominal resistivity

- Substrate losses higher than expected (coplanar devices)

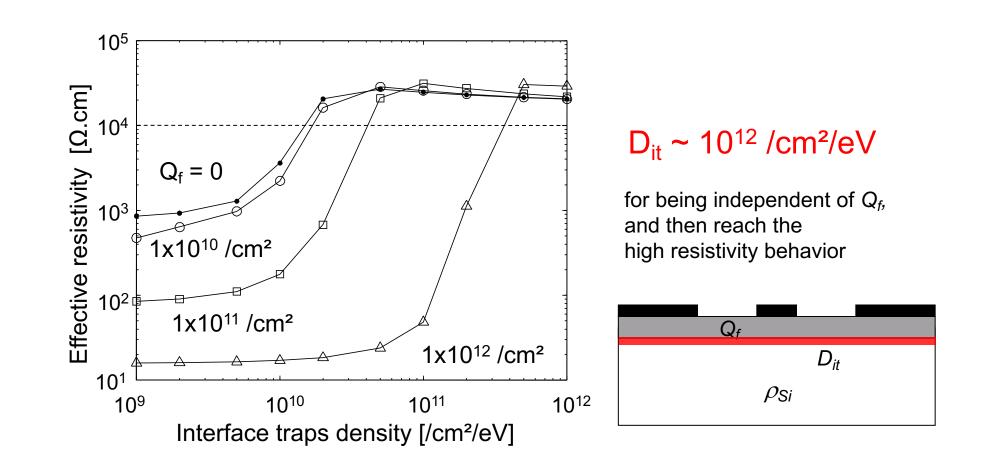

### **Dependence of the effective resistivity**

$$\rho_{\text{eff}} = f(\rho_{\text{Si}}, Q_f, t_{\text{ox}}, V_a, D_{it})$$

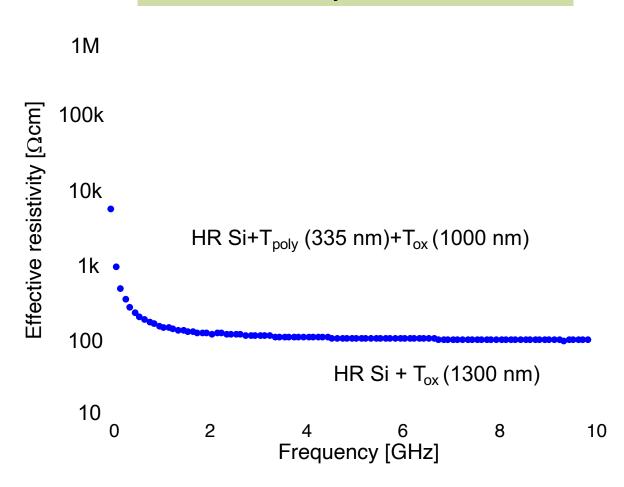

### **Experiments in our academic clean room facilities – it works!**

Effective resistivity of CPW: ~10 kΩ.cm

[D. Lederer, J.-P. Raskin, *IEEE EDL'05*]

### 2005: fundamental academic breakthrough

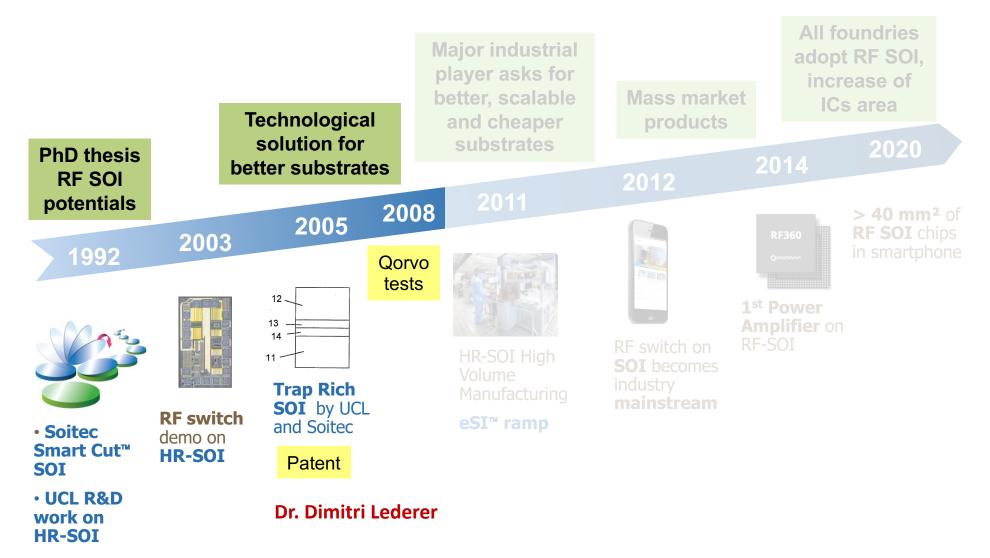

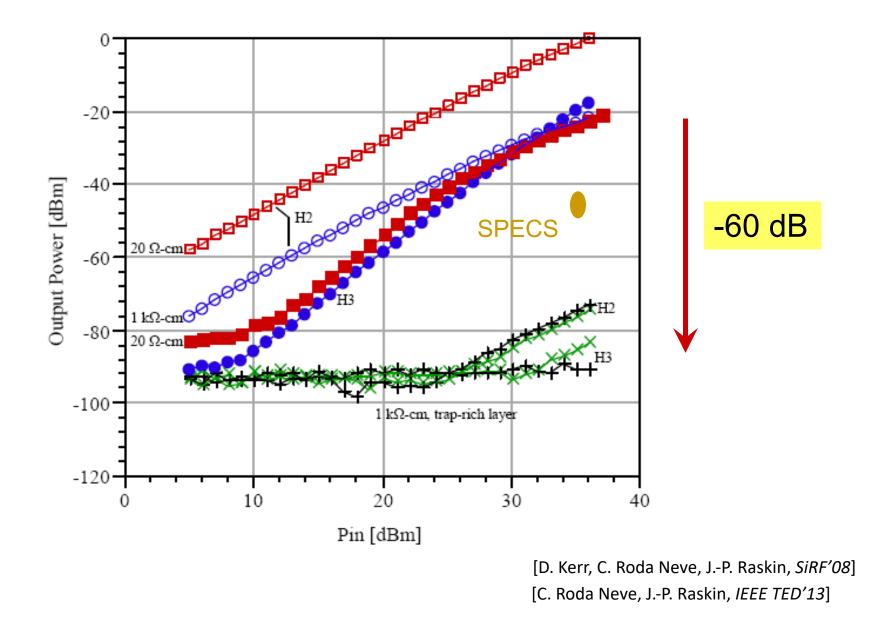

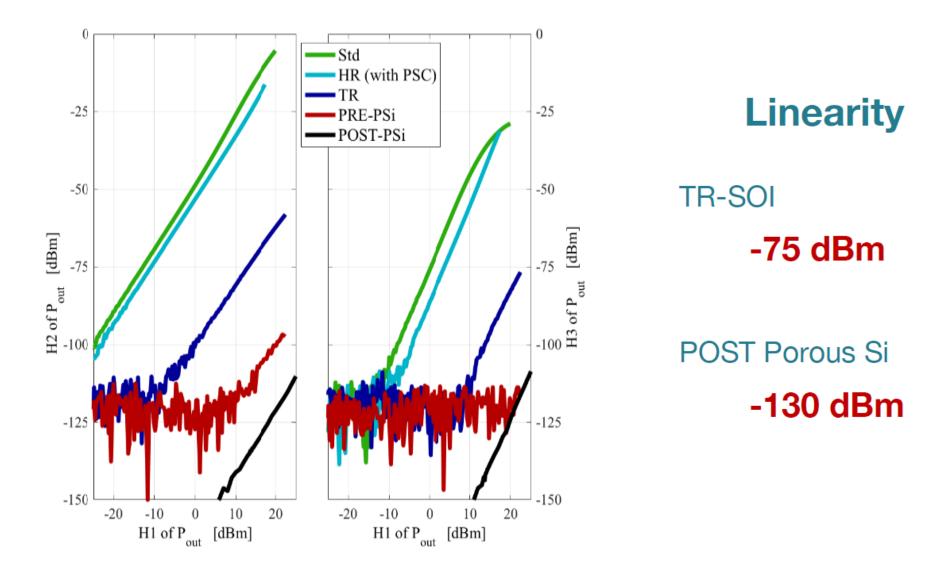

### **2008: call from Qorvo – substrate linearity**

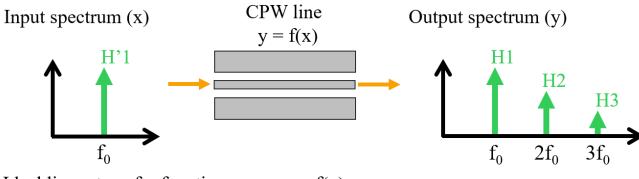

### Si Substrate – Source of non-linearity

Ideal linear transfer function: $y = f(x) = a \cdot x$ Real non-linear transfer function: $y = f(x) = a \cdot x + b \cdot x^2 + c \cdot x^3 + ...$

Semiconductors are non-linear by nature (field-effect)

### 2008: drastic reduction of the substrate non-linearties

### 2008: a long journey to industrialization

### 2008: a long journey to industrialization

15-20 years from discovery to products innovation

- Move to low power mmW frequencies: need for shorter nodes

- Move from PD SOI to FD SOI

- What about the **compatibility of trap-rich** RF-SOI substrate **with FD SOI?**

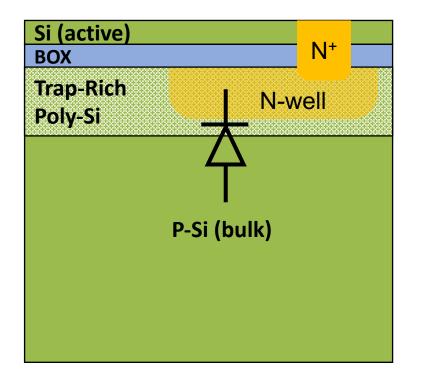

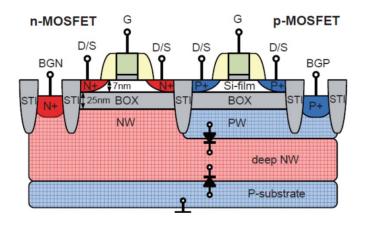

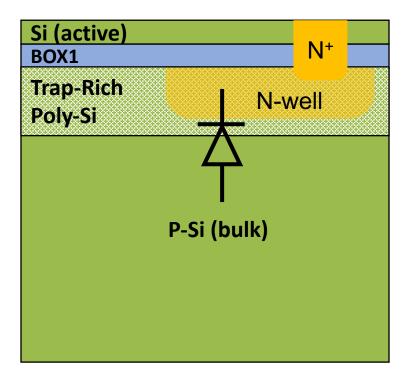

### **Compatibility of trap-rich concept with FD SOI technology?**

FD-SOI offers functionalities below the BOX.

**Back-gates and isolation diodes** will then be defined **in the trap-rich** polysilicon.

Much larger reverse leakage current of PN junction in polysilicon layer.

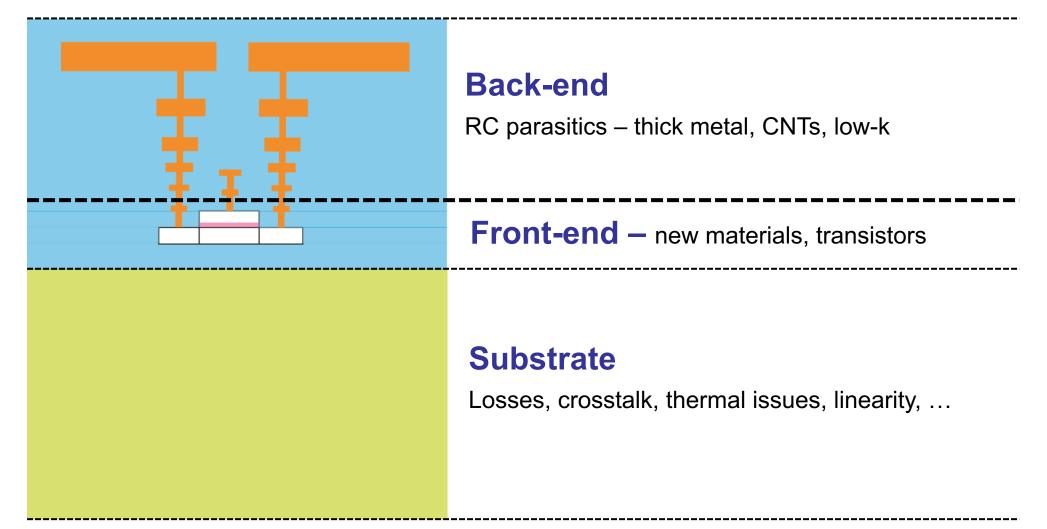

#### **Back-end**

RC parasitics - thick metal, CNTs, low-k

Front-end – new materials, transistors

#### Substrate

Losses, crosstalk, thermal issues, linearity, ...

# New generations of innovative SOI substrates for RF and mm-waves applications

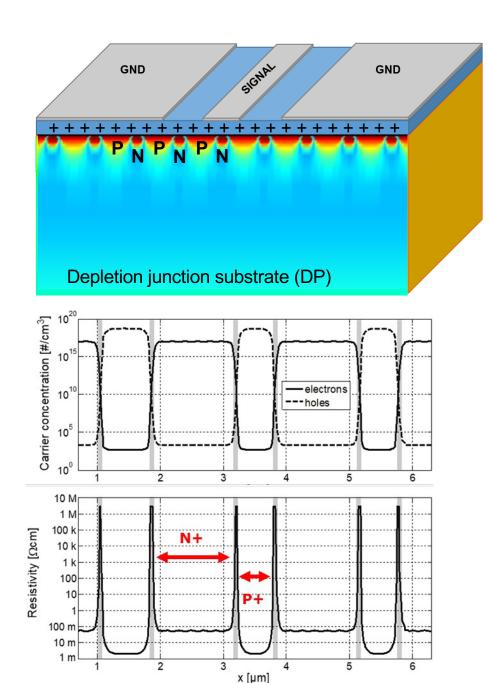

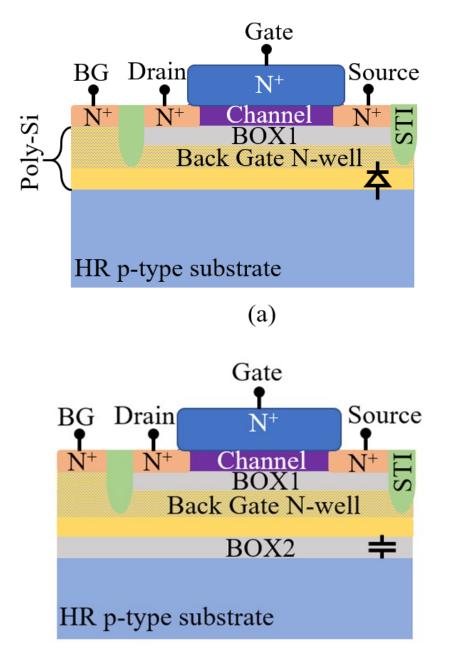

# **Smart PN junctions implanted below the BOX**

### **Deep depletion – Smart PN implants**

[M. Rack et al., IEEE Electron Device Letters, May 2019]

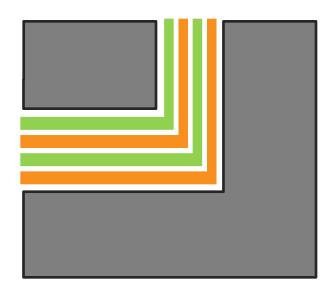

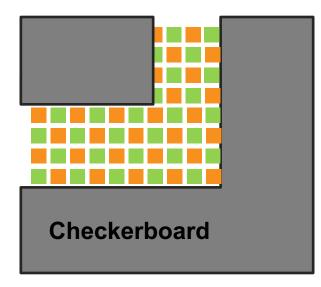

# **Smart PN implants – compatible with FD SOI**

Co-design between circuit layers and substrate layers

Techno layer

P implant

N implant

nt Independency between circuit layers and substrate layers

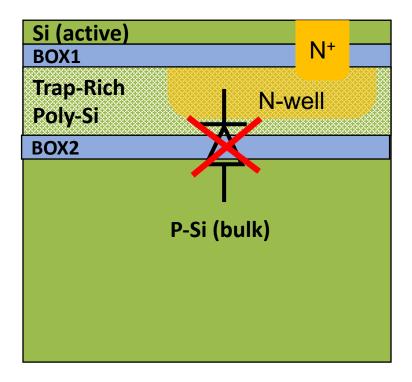

# **Double BOX SOI substrate for**

# enhanced digital and RF functionalities

# **Double BOX SOI substrate for**

# enhanced digital and RF functionalities

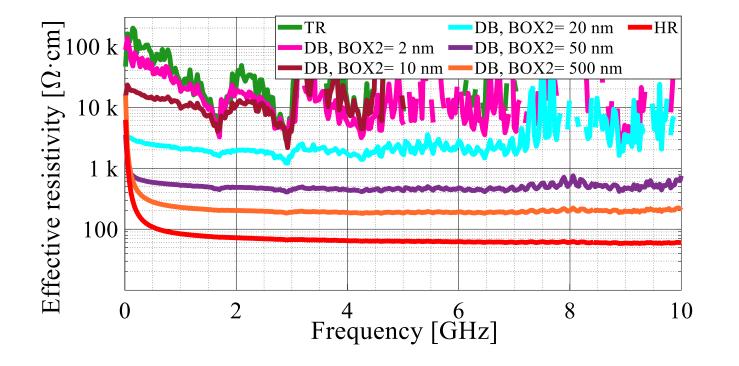

# **Effective Resistivity**

Measured effective resistivity as a function of the frequency for the TR, HR and DB substrates with different BOX2 thicknesses.

With the **increase in BOX2 thickness**, the trap-rich polysilicon layer becomes further away from the BOX2-bulk interface, and the **passivation is less effective**.

If the BOX2 thickness is **thinner than 10 nm**, the **effective resistivity** of the substrate is at least equal to  $10 \text{ k}\Omega \cdot \text{cm}$ .

Therefore, it demonstrates that DB wafer can be **as efficient as TR wafer** if BOX2 is thinner than 10 nm.

# **Digital and RF enhanced features**

- DB SOI substrate combined with high-resistivity handle Si wafer exhibits RF performance similar to the best TR SOI if BOX2 is thinner than 10 nm.

- Thanks to BOX2 layer, TR can be implemented beneath BOX1 without degrading the isolation of the back gate with the handle Si substrate.

- DB SOI substrate offers much larger back gate voltage tuning range thanks to the presence of BOX2 layer underneath the back gate contact. This feature is quite interesting for digital circuits.

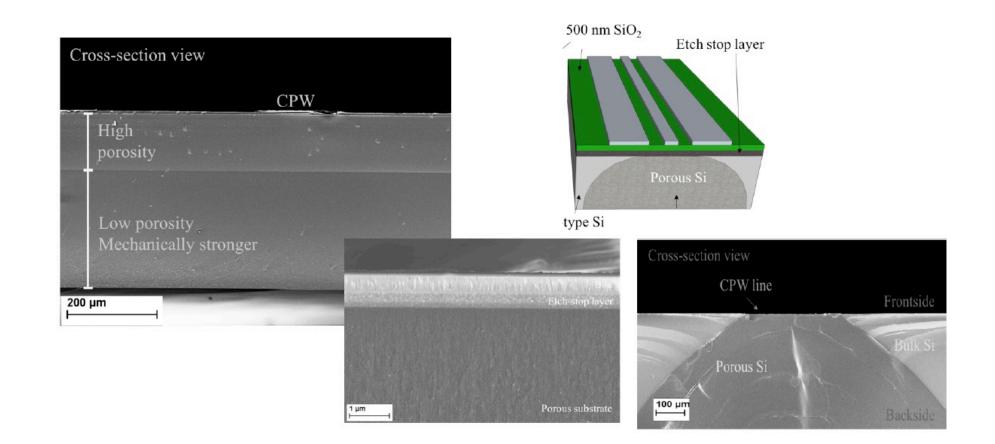

# **Backside porosification of SOI substrate**

### **Porous Silicon in post-CMOS**

[G. Scheen *et al., IEEE International Microwave Symposium 2019*] [M. Rack *et al., IEEE Transactions on Electron Devices,* May 2018]

-----

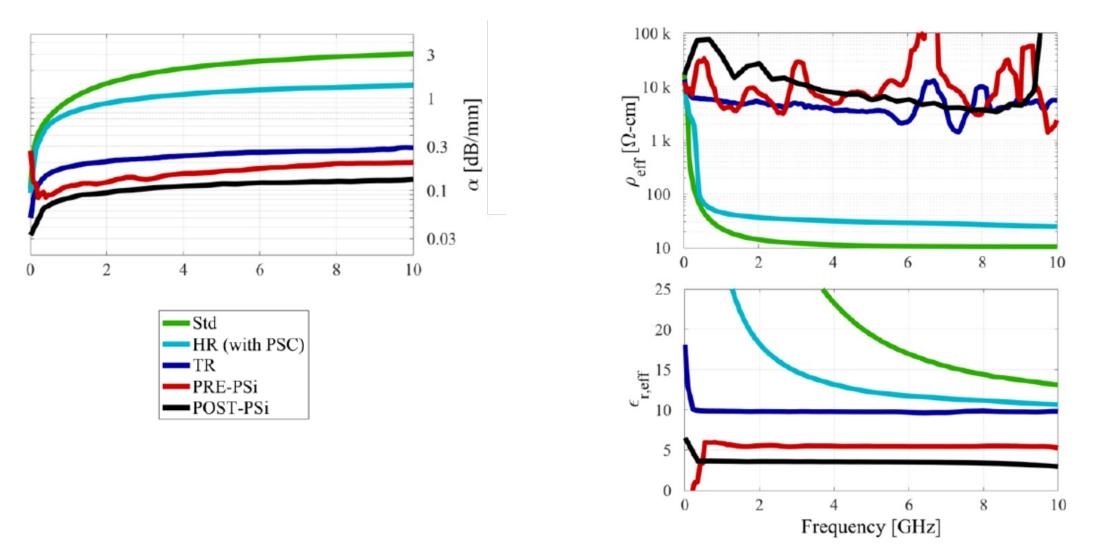

### **Porous Silicon – RF performances**

[G. Scheen et al., IEEE International Microwave Symposium 2019]

[M. Rack et al., IEEE Transactions on Electron Devices, May 2018]

### **Porous Silicon – RF performances**

[G. Scheen *et al., IEEE International Microwave Symposium 2019*] [M. Rack *et al., IEEE Transactions on Electron Devices,* May 2018]

### **Conclusions**

- Trap-rich HR SOI (eSI) presents outstanding RF performance. There is still room for improvement and innovation;

- The benefits of HR Si substrate for FD SOI have been demonstrated. In that case, smart PN implants underneath the thin BOX are used to get rid of the parasitic surface conduction and thus conserve the HR properties of the substrate;

- **Double BOX SOI** substrate demonstrated enhanced digital and RF functionalities;

- Porous Si in post-CMOS leads to substrates characterized by a very high effective resisitivity and low permittivity;

- Today, smart-cut is used to transfer GaN or InP on top of HR Si substrate for serving the high power and high frequency ICs at RF and mmW.

# Acknowledgements

UCLouvain researchers: D. Lederer, V. Kilchytska, M. Rack, L. Nyssens, M. Nabet, A. Halder, Q. Courte, Y. Yan, M. Vanbrabant, M. Moulin, M. Perrosé, P. Cardinael, Y. Bendou, S. Ma, R. Tuyaerts, A. Masrouri, L. Delait.

Inspiring senior researchers: Jean-Pierre Colinge, Sorin Cristoloveanu, Bich-Yen Nguyen