# Advanced porous silicon substrate for RF applications

### **Richard Hammond**

Technology Director, IQE Silicon Compounds (UK)

- Introduction to Porous Silicon

- Porous Silicon Resistivity

- RF Characterisation of Porous Silicon

- Epitaxy on Porous Silicon

- Conclusions

# Introduction to porous silicon

# What is porous silicon?

### **Porous Silicon:**

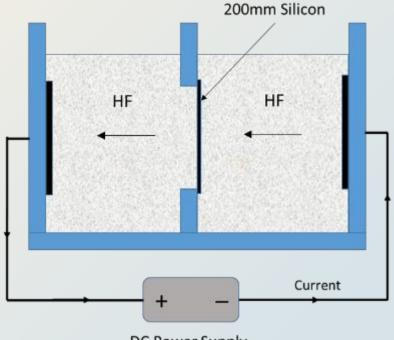

Electrochemical Etch of Silicon in Hydrofluoric Acid.

DC Power Supply

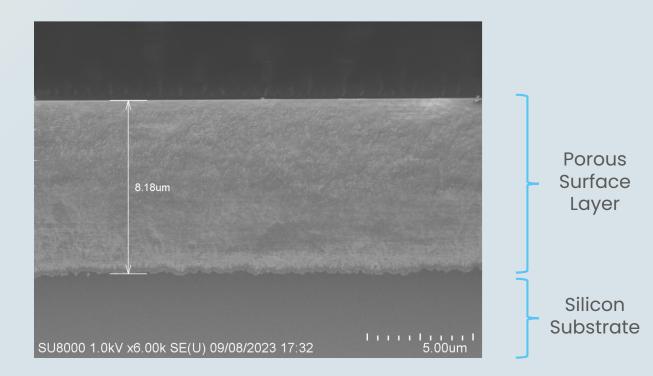

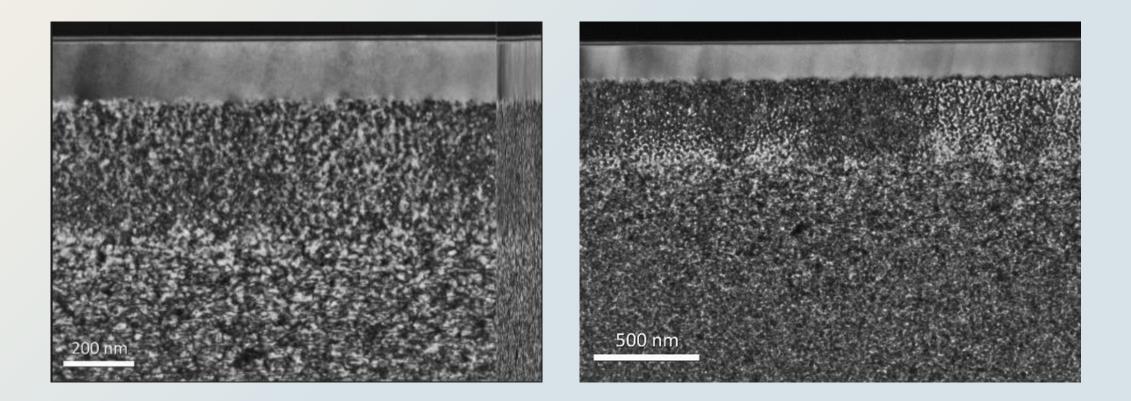

XSEM:

**Etch duration ~ 5mins**

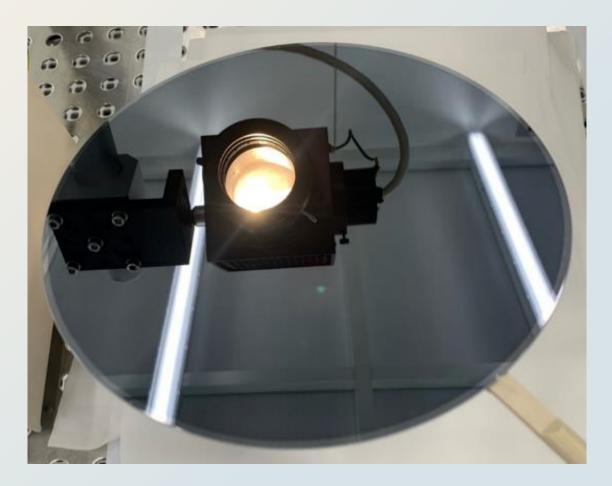

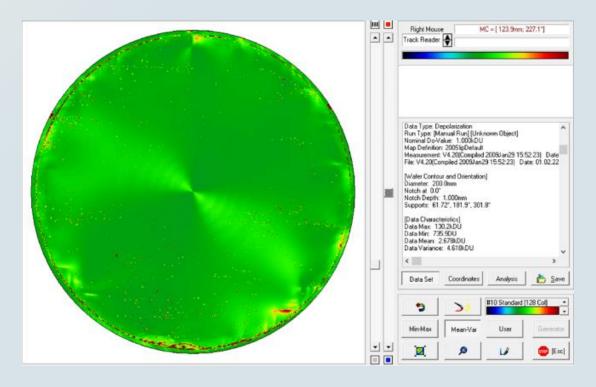

## 200mm porous silicon

- Typical bright light image of a 200mm porous silicon substrate

- Industry standard 3mm edge exclusion

### **Porous silicon**

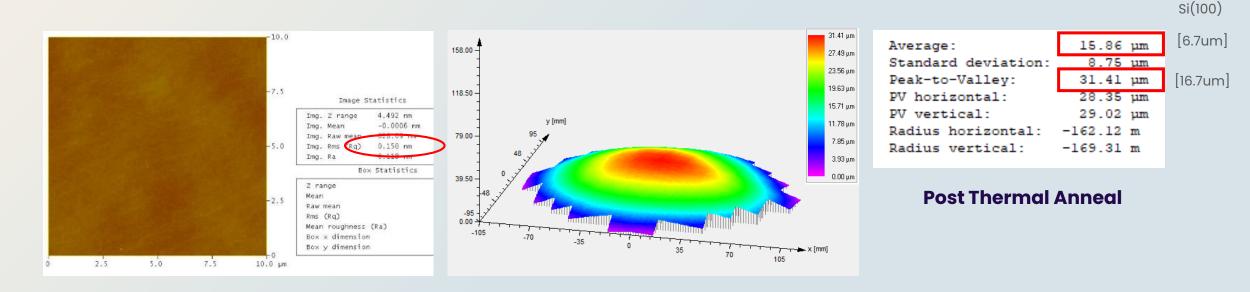

## Roughness & bow

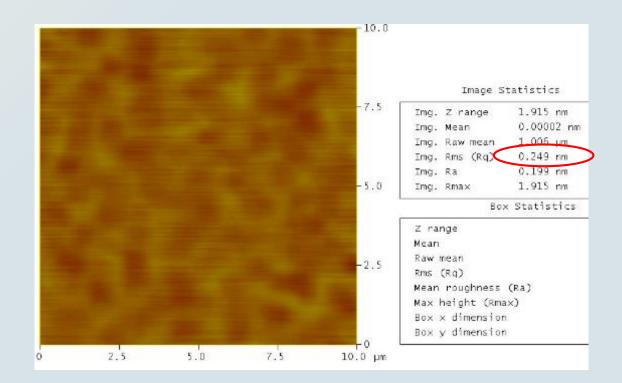

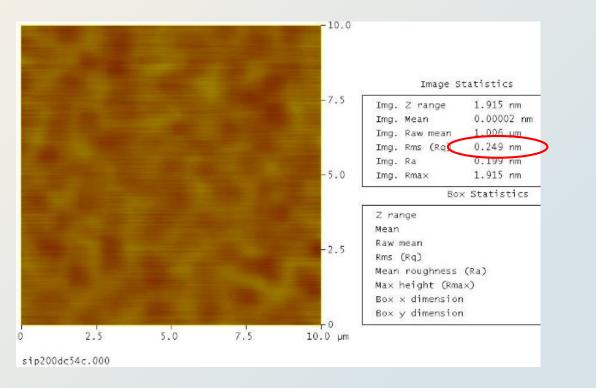

### AFM:

- Ultra smooth surface post porous etch

- On a par with prime silicon surface roughness

# **Porous silicon resistivity**

# **Porous silicon resistivity**

#### Investigations of the Electrical Properties of Porous Silicon

Rolfe C. Anderson, Richard S. Muller, and Charles W. Tobias\* Berkeley Sensor and Actuator Center, Department of Electrical Engineering and Computer Science, University of California, Berkeley, California 94720

J. Electrochem. Soc., Vol. 138, No. 11, November 1991 © The Electrochemical Society, Inc.

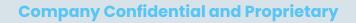

Back in 1991, Anderson described a 'depletion region' surrounding the pores. As these depletion regions merged, the porous silicon became 'fully depleted' of charge carriers.

#### **Quote:**

"For porous silicon formed from a 30–50  $\Omega$ cm boron doped (p-type) substrate, the variations of zero-bias capacitance and conductance indicate (for layers from 0.34 to 4.6  $\mu$ m thick) that the porous layer is fully depleted of free carriers, and the resistivity is 1.6 x 10<sup>7</sup>  $\Omega$ cm".

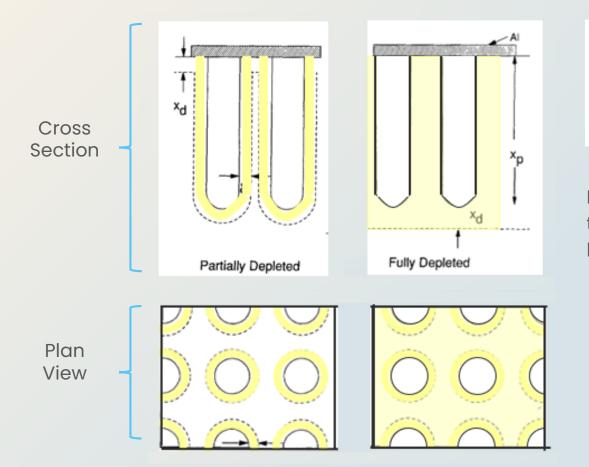

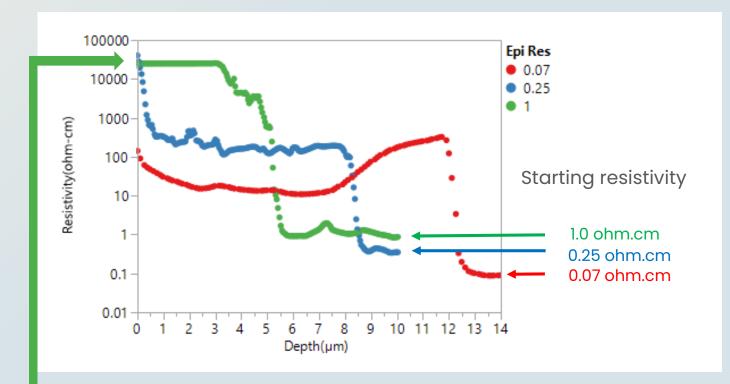

# **Spreading resistance profiling**

Basically a 4pt probe stepped across a ground bevel edge to exaggerate the layer thicknesses.

Carrier depletion regions widen as initial doping level decreases.

At ~1ohm.cm depletion regions merge and porous region becomes 'fully depleted'.

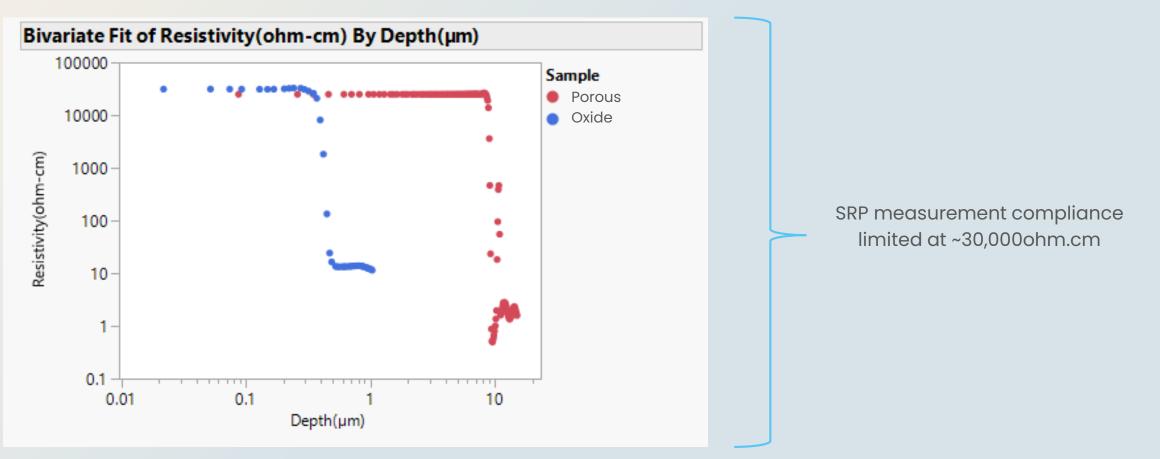

### **Porous vs. thermal oxide**

### 10um Porous vs. 500nm Thermal Oxide

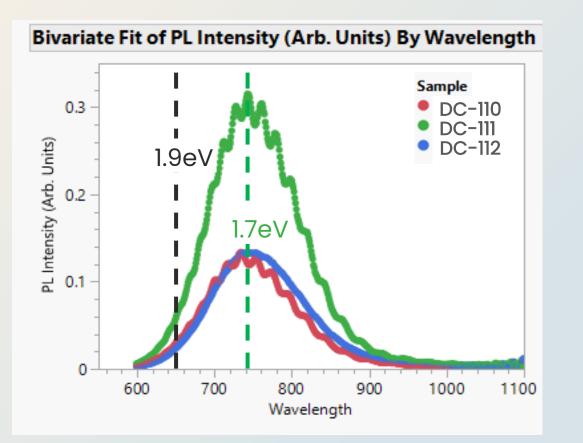

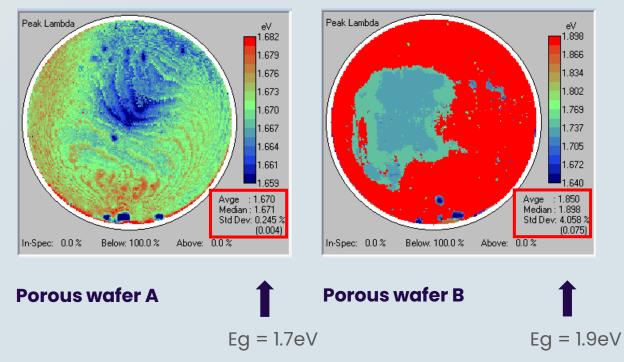

### **Porous silicon PL**

### 31,000 point PL map

Bulk silicon bandgap = 1.1ev

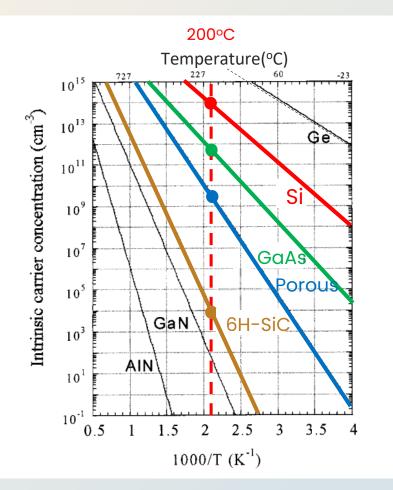

### **Intrinsic carriers**

$$N_i = \sqrt{N_c N_v} exp \left[ -\frac{E_g}{2k_b T} \right]$$

The intrinsic carrier concentration of a semiconductor is exponentially proportional to the bandgap

|        | Semiconductor | Bandgap<br>(eV) | Intrinsic Carrier Concentration<br>at 200C (cm-3) |

|--------|---------------|-----------------|---------------------------------------------------|

|        | Germanium     | 0.67            | 1e16                                              |

|        | Silicon       | 1.12            | 1e14                                              |

|        | GaAs          | 1.42            | 6e11                                              |

| Porous | Porous        | 1.7-1.9         | ~5e9                                              |

|        | 6H-SiC        | 3.02            | 1e4                                               |

At 200C, Porous Silicon with Bandgap of 1.9eV would have 4-5 orders of magnitude fewer thermally generated free charge carriers than high resistivity silicon with a bandgap of 1.1eV

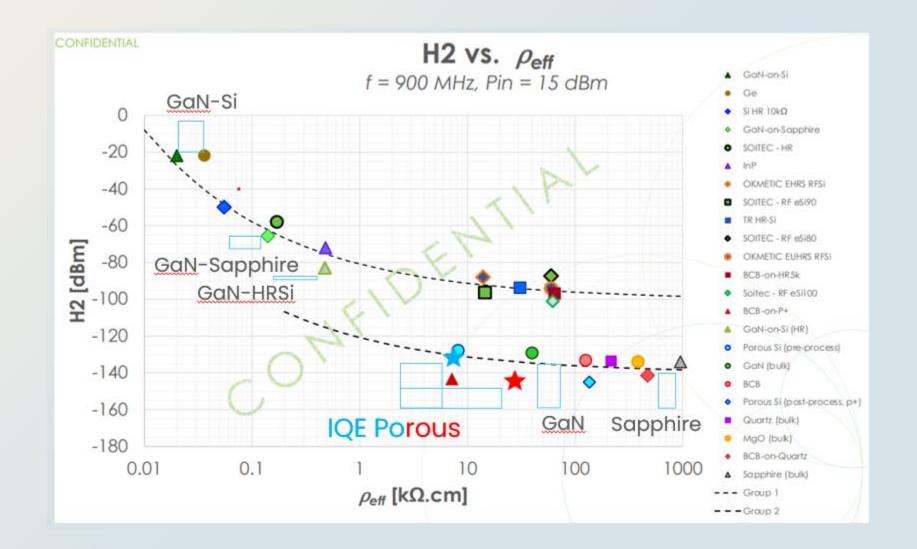

# RF characterisation of porous silicon

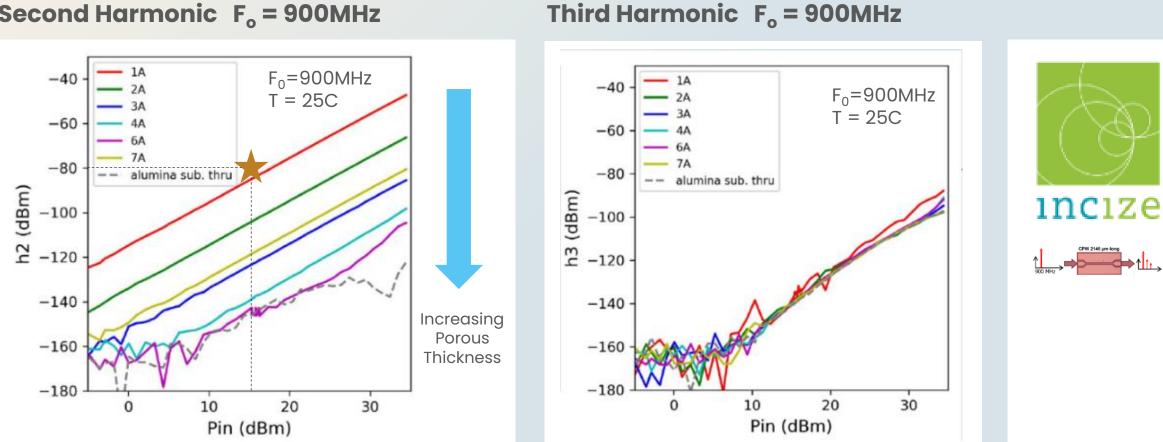

### **Porous harmonics vs. Thickness**

Second Harmonic  $F_0 = 900 MHz$

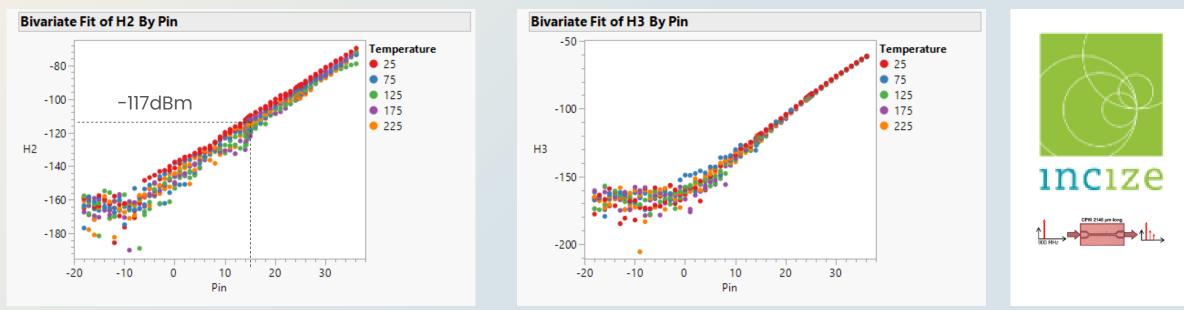

### **Porous harmonics vs. temp**

### $F_o = 900MHz$

$[F_o = 900 Mhz]$  H2 and H3 linear and stable to Pin = 36dBm and up to 225C

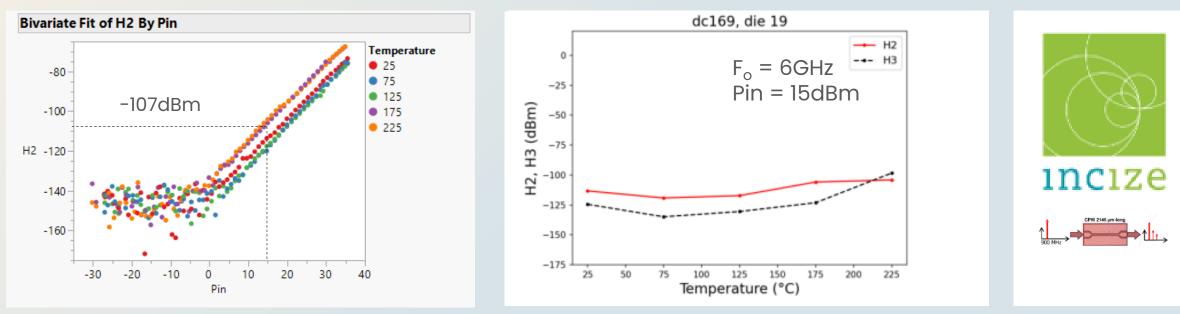

### Porous harmonics @ 6GHz

### $F_o = 6GHz$

$[F_o=6GHz]$  H2 and H3 linear and stable to Pin = 36dBm and up to 225C

## **Intrinsic carriers**

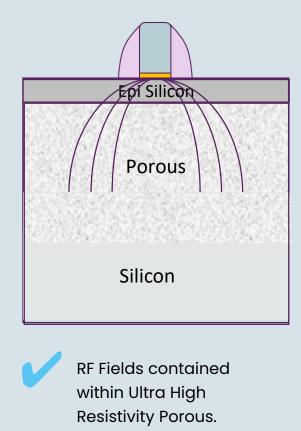

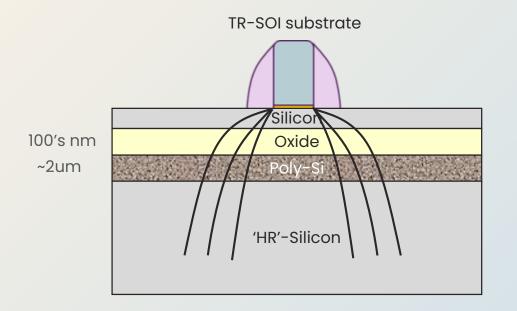

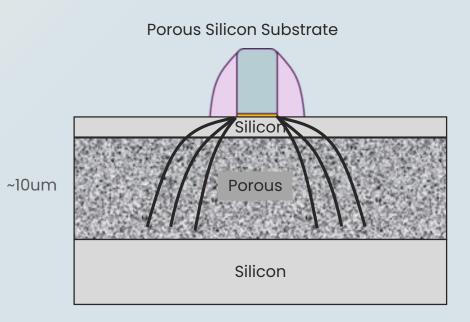

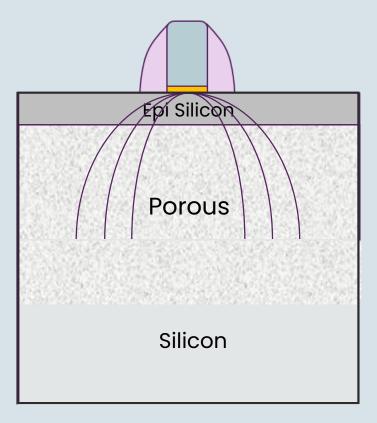

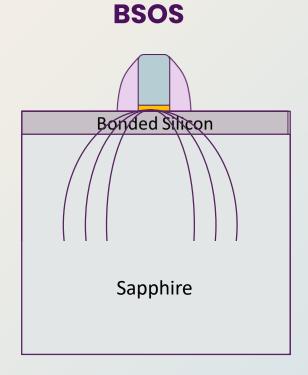

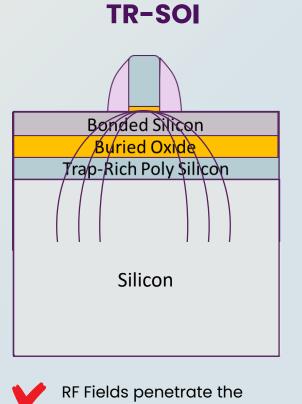

- RF fringing fields penetrate into the 'High Res' silicon substrate.

- Silicon has a low bandgap of 1.1eV.

- At device operating temperatures, significant amount of intrinsic carriers are generated:

- lel4cm<sup>-3</sup> @ 200C

- 150ohm.cm

- High Res substrate is not so high res at device temps !

- RF fringing fields confined within thick porous silicon layer.

- Porous Silicon has an increased bandgap of 1.9eV.

- At device operating temperatures, minimal thermal carriers are generated

- 5e9cm<sup>-3</sup> @ 200C

- >100,000 ohm.cm

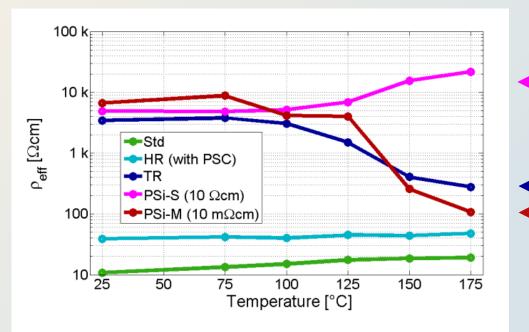

### Literature

### Rack et al, UCL

Fig. 6. Effective resistivity averaged between the beginning of the quasi-TEM mode (different for each substrate) and 10 GHz and extracted at different temperature points ranging from 25 °C to 175 °C for the five Si-based substrates. Rack et al have compared the effective resistivity of various substrates as a function of temperature.

The porous (FD) silicon maintains its Effective Resistivity up to 175C.

Note the large degradation in effective resistivity of **Trap Rich** and **Porous (non-FD)** substrates as a function of temperature.

# Epitaxy on porous silicon

# 200mm epi on porous

#### As etched

Post 180nm epi

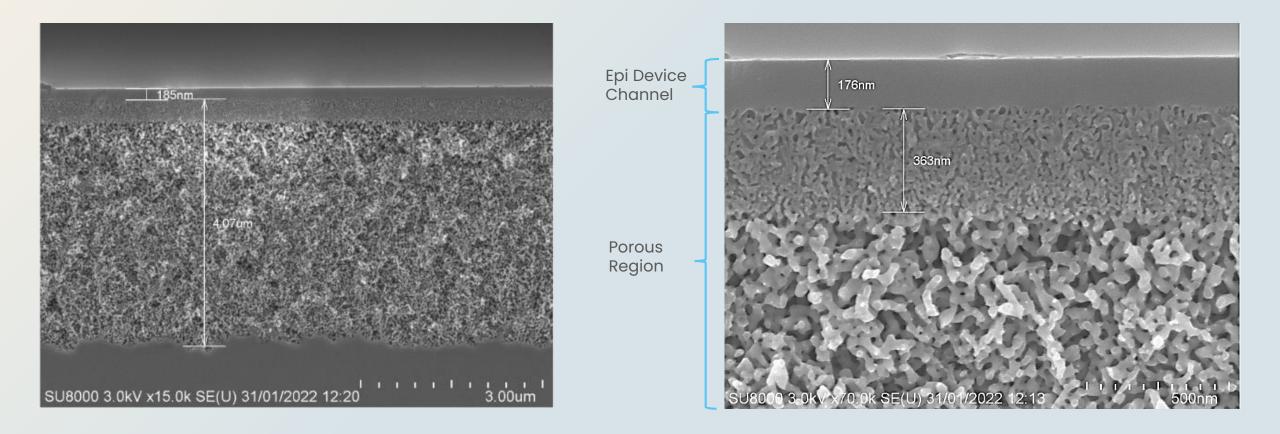

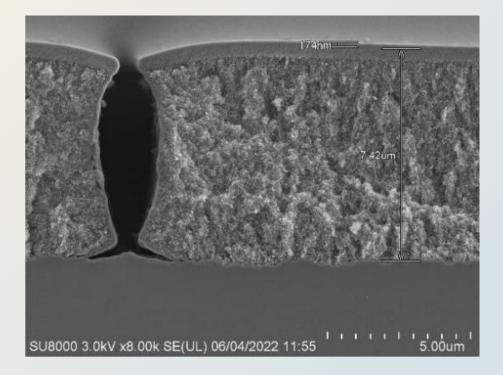

# Epitaxy on porous silicon (SEM)

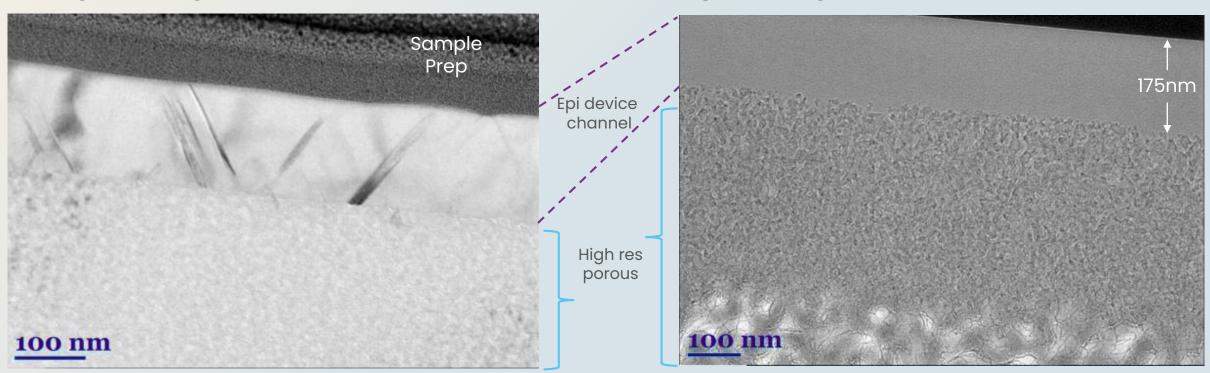

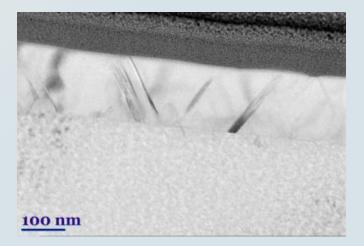

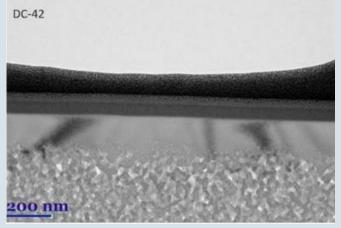

# **Epitaxial defects (TEM)**

### Non optimised process

#### High defectivity epi

Defect free epi

**Optimised process**

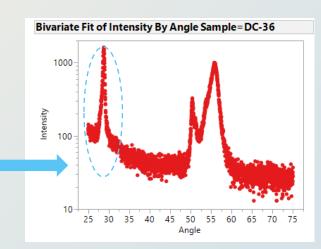

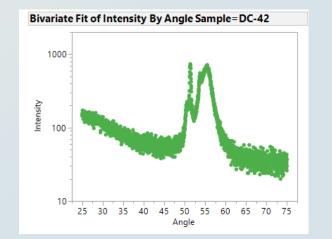

# **Grazing angle X-ray diffraction**

#### High defectivity epi

XRD Peak apparent in defective silicon due to different crystallographic orientations

#### **Defect free epi**

### **i**QE

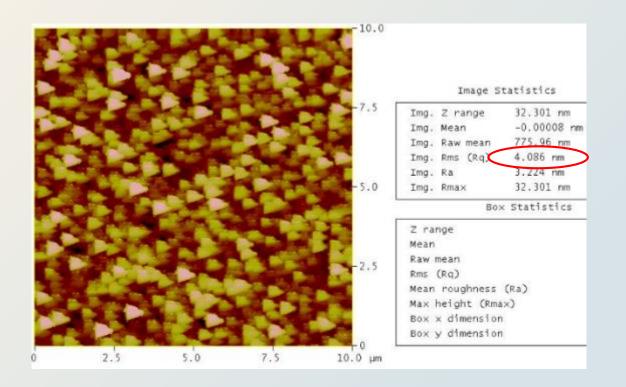

# Epi surface roughness (AFM)

#### High defectivity epi

#### Defect free epi

- Epi Surface Roughness = 0.25nm

- Comparable to Prime Silicon wafer

# **Epi on thin porous**

#### Sub-nm surface roughness

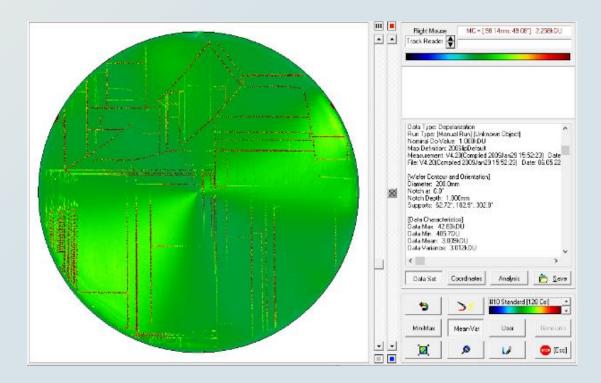

### Scanning transmission IR image (TePla)

#### No cracking observed at < 5um porous thickness

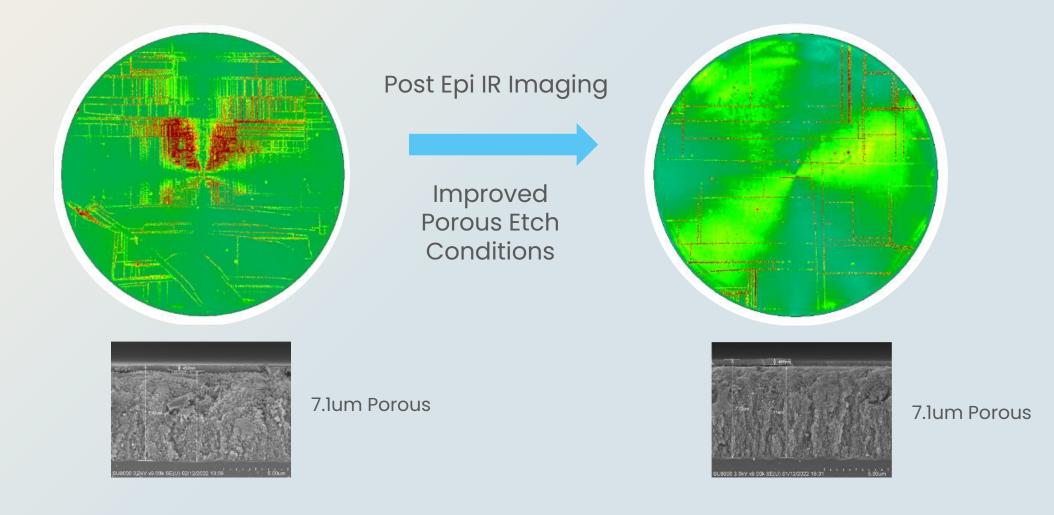

# **Epi on thick porous**

Cracking observed at Porous Thickness ~8um

Scanning Transmission IR Image (TePla)

# **Etch optimisation**

### Conclusion

### Porous silicon excellent candidate for RF applications:

- Carrier depletion leads to ultra-high resistivity.

- Excellent Harmonic Performance.

- Increased Porous Bandgap leads to significant reduction in thermally generated free carriers:

- Linear RF Performance up to 225C.

Porous silicon acts like an amorphous dielectric, but maintains its crystallographic nature:

- Ability to grow single crystal, defect-free, device channels.

- Channel thickness uniformity dictated by epi.

**Company Confidential and Proprietary**

# Epi on porous

RF Fields contained within fully insulating sapphire.

High resistivity silicon.

Porous